Then again synthesis may end up with the same circuit in the end. Haven't tried synthesizing both my preferred version and the modified original, but it seems to me the one with the feedback might result in something slightly slower as the bi bits have to propagate through the bit width of the converted value. GitHub - jquerius/ieee-convert: A simple routine in Verilog HDL that converts integers into IEEE 754 Floating Point format. Note: this gray to binary conversion doesn't require the feedback of the bi to produce the bi bit (it only relies on the gray value). A simple routine in Verilog HDL that converts integers into IEEE 754 Floating Point format. Weve discussed essential functions for real number conversions, signedness conversions, and dynamic casting. g (gray ) ) initial begin $monitor ( "binary = %b, gray = %b, binary %b", bin, gray, binary ) end endmodule Conversion functions in Verilog and SystemVerilog offer designers a convenient way to manage and convert different data types in their designs. `timescale 1ns / 1ps module tb parameter N = 4 reg bin wire gray wire binary initial beginīin = bin + 1 end end // my preferred versions of both conversions // binary to gray In order to compare results, all of the numbers were checked with an online IEEE 754 float converter. We can this program by breaking it into functions that allow us to run different values through it. The sign bit was set at the beginning of the program when we determined whether to flip the bits of the LHS register from 2’s complement. Verilog - Representation of Number Literals(cont. This tells us the number of shifts that need to be performed in order to reconstruct the floating-point number from IEEE format.

The exponent value comes from the length that the most-significant 1-bit is in. This gives us a complete mantissa value for the result.

If there are, we should round the last bit of the mantissa to 1. We can use a module to do this, which will output the decimal number as a 4-bit binary number. If the RHS value gets shifted too far to the right and we lose precision, we need to check if there are any 1-bits to the right of where the value gets cut off. First, we need to read the input from the 4x4 matrix keypad. Since we stored our fraction starting in the MSB, we take the value from that register, shift it to the right however many binary digits the left value takes up, and OR the mantissa LHS value with the RHS fraction. The RHS fractional value must be combined with the LHS value already stored in the result register.

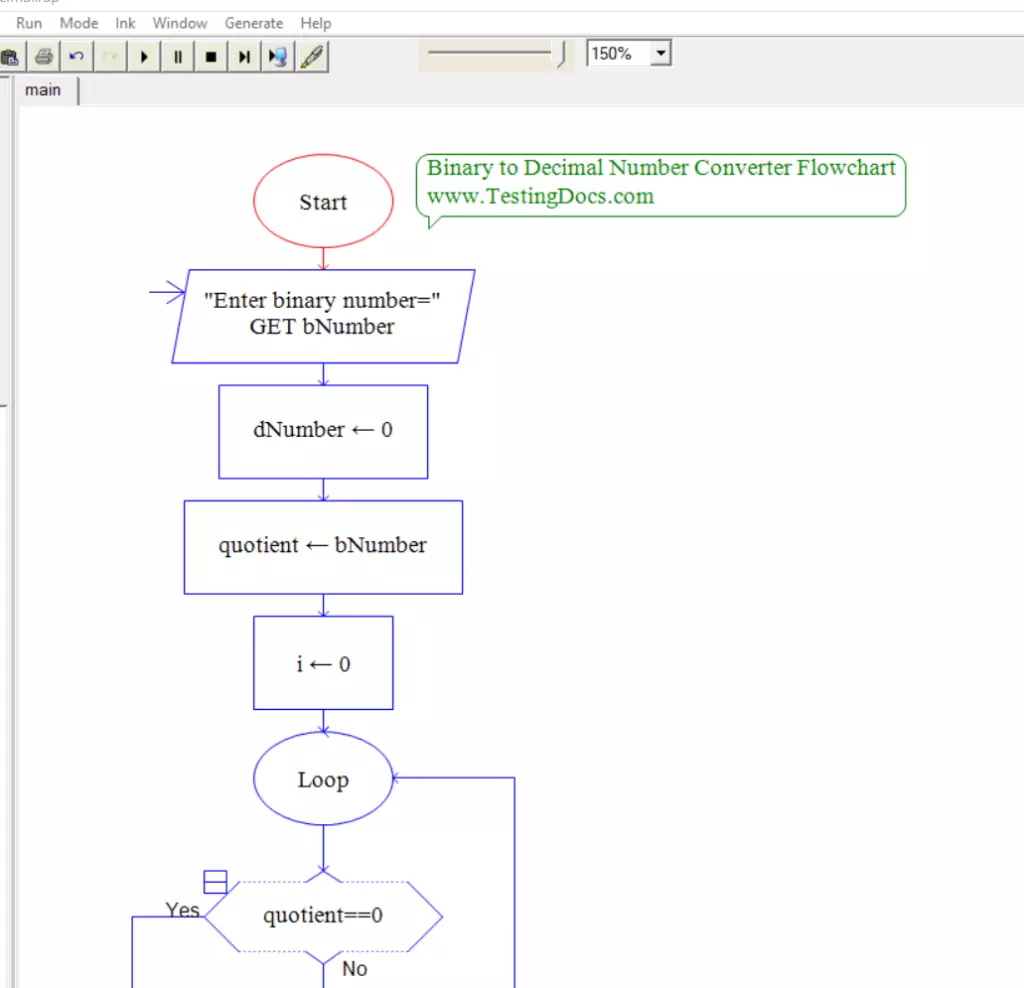

The rightmost digit equals to 2 0 (1), the next one equals to 2 1 (2), the next one equals to 2 2 (4) and the leftmost one. Step 2: Each hex digit represents four binary digits and therefore is equal to a power of 2. In verilog, all the data types are just collection on bits. Then we apply the AND operation to the mask and the LHS value, and shift the result into the most significant bit for the mantissa value (position 22). If there are any, change the hex values represented by letters to their decimal equivalents. Easy Conversion is automatic in verilog if you assign to an integer. To get the mantissa value, if there is a value in the left-hand argument, we find the most significant 1-bit and create a bit mask that is the length of the value excluding the most significant 1-bit. Knowing this value allows us to treat the integer value like a decimal so that we can use a doubling technique to find its binary fractional approximation. Binary coded decimal is used to represent a decimal number with four bits. We do this by finding a power of 10 that is greater than the RHS argument. This module takes an input binary vector and converts it to Binary Coded Decimal (BCD). The RHS is passed in as an integer, so we need to convert it to a binary fraction. We convert the left-hand argument to a positive binary number even if it was stored as a negative (2’s compliment). The only issue is to make sure that your compiler knows you are giving it a double-precision number than an integer, but this will most likely be done in the same way it accepts double-precision binary numbers. The following approach was used to generate a floating point number: The numbers are stored as bits in the system either way, so all operations in your processor, FPGA, etc., happen in binary. The following article discusses exactly what a floating point number is. A simple routine in Verilog HDL that converts integers into IEEE 754 Floating Point format.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed